I0: ADD R2, R0,R1 (The operation is R2←R0+R1)

I1: SUB R5, R3,R4 (The operation is R5←R3-R4)

I2: MUL R2, R5,R2 ( The operation is R2←R5*R2)

I3: DIV R5, R2,R6 (The operation is R5←R2/R6 )

What is the number of clock cycles needed to execute the above sequence of instructions?

SUB r1, r2, r3

MUL r1, r2, (r3)

DIV r1, r2, @(r4)

Suppose every instruction is one word long, as well as every address.

(a+b)+(e-(c+d))*f

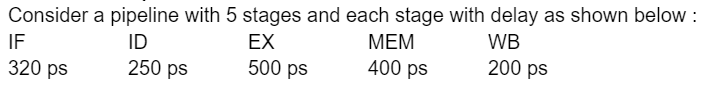

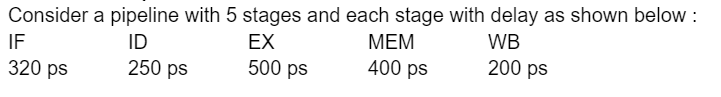

How long will it take to completely process two software instructions in a pipelined processor?

Try to improve performance of the above pipeline, you have decided to break up 2 of the above stages into half. What is the maximum speedup achieved in the new pipeline system to execute two instructions?